The E3AI summer school is open to second year Master students, doctoral students, post-doctoral fellows, researchers and professionals with an interest in embedded artificial intelligence, deep learning, neuromorphic computing, natural language processing, spintronics and 6G communications.

Course content will address the consequent skill gap between embedded technology and deep learning applications, and will equip participants with the interdisciplinary knowledge and skills needed to develop innovative circuit architectures and execute data intensive applications on resource-constrained devices.

This summer school is supported by FVLLMONTI, Hermes and RadioSpin, three H2020 European projects, and is co-organised with the Green AI (GrAI) chair in artificial intelligence and the IEEE Circuits and Systems Society. The event is the first in a series of similar bi-annual events organised by and for the Embedded Artificial Intelligence (EAI) transdisciplinary community.

Course content will address the consequent skill gap between embedded technology and deep learning applications, and will equip participants with the interdisciplinary knowledge and skills needed to develop innovative circuit architectures and execute data intensive applications on resource-constrained devices.

This summer school is supported by FVLLMONTI, Hermes and RadioSpin, three H2020 European projects, and is co-organised with the Green AI (GrAI) chair in artificial intelligence and the IEEE Circuits and Systems Society. The event is the first in a series of similar bi-annual events organised by and for the Embedded Artificial Intelligence (EAI) transdisciplinary community.

• IMS Lab •

351 Cours de la Libération, 33405 Talence Cedex, France

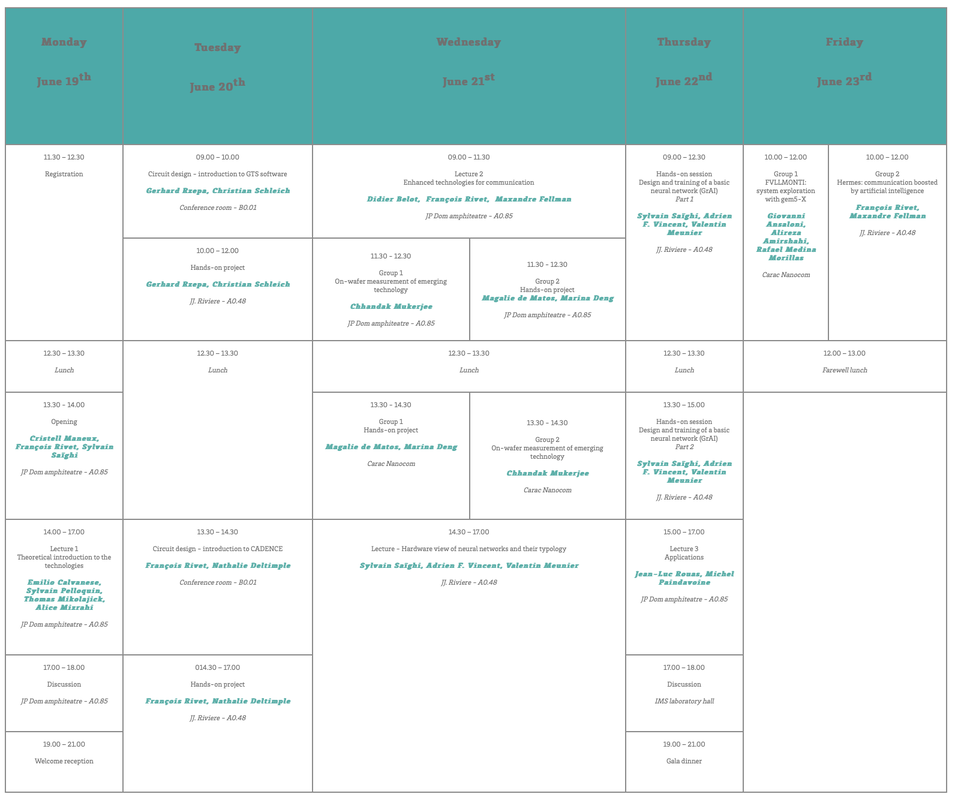

Programme

Timetable and learning outcomes

|

|

|

Artificial intelligence and deep learning applications currently require consequent amounts of computing resources that are not easily accessible for low-latency applications handling sensitive data. Massive data sources have to be pushed to multiple high-speed computers in remote server farms, raising serious concerns related to security and privacy. A possible solution comes from executing machine learning models on embedded devices, a topic generally known as “Embedded Artificial Intelligence”. This calls for a close integration of software and hardware solutions with highly optimised machine learning models and a new generation of lightweight, energy-efficient embedded hardware suitable for executing neural networks on edge devices.

The educational objectives of the summer school reflect the highly interdisciplinary nature of the Embedded Artificial Intelligence research theme, covering on the one hand topics related to fabrication, characterisation, modelling, design, simulation and exploration of neuromorphic devices; and on the other hand application-specific topics including speech and text processing, 6G communications, and radio frequency oscillators. The core objective of the summer school is to cover hardware-related aspects of neural networks while aiming to provide participants with a basic understanding of neural network implementation. |

Lecture 1 - Theoretical introduction to the technologies

The objective of this lecture is to present various state of the art technologies for Embedded Artificial Intelligence.

Part 1: The first part of the lecture will introduce vertical nanowire field-effect transistors (VNWFETs), a promising candidate for building blocks that enable 3D neuromorphic computing, increasing device performance and density. These innovative transistors can be configured as 3D stacked hardware layers that closely mirror the architecture of a typical neural network.

Part 2: This talk will first present a very short overview of the major analog and RF technology features of the 28nm FDSOI planar CMOS technology. The benefits of FD-SOI technology for analog/RF circuits will then be discussed, with a focus on IoT applications. Attendees will learn about design techniques that take full advantage of the unique capabilities of FD-SOI, including body biasing to efficiently modulate on the fly SoC solutions from high performance operation to energy efficiency mode. This further enhances the excellent analog/RF performances of these devices. The second part of this presentation will focus on novel design techniques that take full benefit of the new fourth transistor electrode (the body tie) and permit to get concurrent solutions that overcome the existing state of the art.

Part 3: This short lecture will provide an overview of how one can use the physics of spintronic nanodevices to implement various functions commonly found in neural networks, e.g., activation function, synaptic weight, multiply-and-accumulate (MAC) operation, etc. Exploiting the richness of intrinsic behaviours offered by such a technology could pave the way for low-latency and low-energy hardware implementations of neural networks, in particular for RF signal processing.

Part 4: Yumain, formerly Global Sensing Technologies, is one of the French leaders in embedded artificial intelligence including sensors and neural networks (edge-computing). This presentation will provide an overview of the industrial applications that require embedded artificial intelligence.

Hands-on session - Circuit design with CADENCE

Cadence is a leading EDA and Intelligent System Design provider delivering hardware, software, and IP for electronic design. Students will learn the basis of integrated circuit design using AMS 0.35um technology with the simulation of an inverter. They will play on transistor dimensions, observe the electrical characteristics by several kind of simulations and draw conclusions.

Hands-on session - Circuit design with GTS

The GTS framework provides a sophisticated graphical user interface that allows users to design 3D nano structures. Participants will learn how to view and analyse simulation results.

Lecture - On-wafer measurement of emerging technology

This tutorial will cover dedicated DC and RF measurement techniques for on-wafer characterization of emerging technologies such as vertical nanowire transistors. Particular focus will be given to novel parameter extraction methods for important device parameters such as threshold voltage, thermal impedance, traps, gate capacitances and test-structure parasitic elements. The lecture will cover the theoretical premise for several of these methods while the practical session will offer hands-on experience with some of these techniques in an experimental environment.

Hands-on session - On-wafer measurement of emerging technology

In this session, participants will be able to visit the IMS characterisation room and learn more about on-wafer measurements directly in the lab.

Lecture - Hardware view of neural networks and their typology

This talk will introduce the event-based computing paradigm for neural networks. This computational approach requires few operations and is inherently suitable for embedded artificial intelligence. After presenting the interest of low power in artificial intelligence, the presentation will review existing industrial products, which will show the interest to pursue a research effort in the field of neuromorphics. The presentation will deal with both inference and learning, based on concrete cases from research work carried out at the IMS.

Hands-on session - Design and training of a basic neural network

In this session, we will use a user-friendly simulator of spiking neural networks. This simulator will allow students to play with the different parameters of the network for a training on a standard database. The neural networks constituted should be consistent with the technological elements discussed in the previous days.

Lecture - Applications

This lecture highlights three separate applications of Embedded Artificial Intelligence including speech recognition and machine translation, 6G communications, as well as image recognition in industrial context (e.g. RF fingerprints and breast cancer). The goal of the first application is to build a lightweight in-ear device that allows on-device speech-to-speech translation, without requiring internet connectivity. The second application is motivated by the fact that Radio Frequency Integrated Circuits (RFIC) have made it possible to democratise communications with ever-greater data exchanges, allowing an increase in communication potential from one generation with 6G in sight and beyond.

Hands-on session – FVLLMONTI Demonstrator - System exploration with gem5-X

During this session, students will be introduced to the gem5-X system simulator and its main features. A hands-on tutorial will allow attendees to acquire experience in simulating the execution of AI applications on complex systems, identify bottlenecks and deploy hardware and software optimization strategies.

Hands-on session - Hermes Demonstrator - Linearization of radio frequency power amplifiers

A novel concept for linearization of Radio Frequency (RF) Power Amplifiers (PAs) will be presented. The Walsh Transform is used for both a conversion scheme from digital to analogue and as a computational basis for evaluating a digital PA predistorter (DPD) model. The mathematical properties of the Walsh theory are exploited to enhance the convergence speed of conventional DPD algorithms and reduce their computational complexity. An experimental demonstration exhibits the performances of a broadband PA’s DPD with simulations and measurements results of a 3-4GHz PA. For similar accuracy, the proposed method converges as fast as conventional algorithms with linear computational complexity instead of quadratic one.

The objective of this lecture is to present various state of the art technologies for Embedded Artificial Intelligence.

Part 1: The first part of the lecture will introduce vertical nanowire field-effect transistors (VNWFETs), a promising candidate for building blocks that enable 3D neuromorphic computing, increasing device performance and density. These innovative transistors can be configured as 3D stacked hardware layers that closely mirror the architecture of a typical neural network.

Part 2: This talk will first present a very short overview of the major analog and RF technology features of the 28nm FDSOI planar CMOS technology. The benefits of FD-SOI technology for analog/RF circuits will then be discussed, with a focus on IoT applications. Attendees will learn about design techniques that take full advantage of the unique capabilities of FD-SOI, including body biasing to efficiently modulate on the fly SoC solutions from high performance operation to energy efficiency mode. This further enhances the excellent analog/RF performances of these devices. The second part of this presentation will focus on novel design techniques that take full benefit of the new fourth transistor electrode (the body tie) and permit to get concurrent solutions that overcome the existing state of the art.

Part 3: This short lecture will provide an overview of how one can use the physics of spintronic nanodevices to implement various functions commonly found in neural networks, e.g., activation function, synaptic weight, multiply-and-accumulate (MAC) operation, etc. Exploiting the richness of intrinsic behaviours offered by such a technology could pave the way for low-latency and low-energy hardware implementations of neural networks, in particular for RF signal processing.

Part 4: Yumain, formerly Global Sensing Technologies, is one of the French leaders in embedded artificial intelligence including sensors and neural networks (edge-computing). This presentation will provide an overview of the industrial applications that require embedded artificial intelligence.

Hands-on session - Circuit design with CADENCE

Cadence is a leading EDA and Intelligent System Design provider delivering hardware, software, and IP for electronic design. Students will learn the basis of integrated circuit design using AMS 0.35um technology with the simulation of an inverter. They will play on transistor dimensions, observe the electrical characteristics by several kind of simulations and draw conclusions.

Hands-on session - Circuit design with GTS

The GTS framework provides a sophisticated graphical user interface that allows users to design 3D nano structures. Participants will learn how to view and analyse simulation results.

Lecture - On-wafer measurement of emerging technology

This tutorial will cover dedicated DC and RF measurement techniques for on-wafer characterization of emerging technologies such as vertical nanowire transistors. Particular focus will be given to novel parameter extraction methods for important device parameters such as threshold voltage, thermal impedance, traps, gate capacitances and test-structure parasitic elements. The lecture will cover the theoretical premise for several of these methods while the practical session will offer hands-on experience with some of these techniques in an experimental environment.

Hands-on session - On-wafer measurement of emerging technology

In this session, participants will be able to visit the IMS characterisation room and learn more about on-wafer measurements directly in the lab.

Lecture - Hardware view of neural networks and their typology

This talk will introduce the event-based computing paradigm for neural networks. This computational approach requires few operations and is inherently suitable for embedded artificial intelligence. After presenting the interest of low power in artificial intelligence, the presentation will review existing industrial products, which will show the interest to pursue a research effort in the field of neuromorphics. The presentation will deal with both inference and learning, based on concrete cases from research work carried out at the IMS.

Hands-on session - Design and training of a basic neural network

In this session, we will use a user-friendly simulator of spiking neural networks. This simulator will allow students to play with the different parameters of the network for a training on a standard database. The neural networks constituted should be consistent with the technological elements discussed in the previous days.

Lecture - Applications

This lecture highlights three separate applications of Embedded Artificial Intelligence including speech recognition and machine translation, 6G communications, as well as image recognition in industrial context (e.g. RF fingerprints and breast cancer). The goal of the first application is to build a lightweight in-ear device that allows on-device speech-to-speech translation, without requiring internet connectivity. The second application is motivated by the fact that Radio Frequency Integrated Circuits (RFIC) have made it possible to democratise communications with ever-greater data exchanges, allowing an increase in communication potential from one generation with 6G in sight and beyond.

Hands-on session – FVLLMONTI Demonstrator - System exploration with gem5-X

During this session, students will be introduced to the gem5-X system simulator and its main features. A hands-on tutorial will allow attendees to acquire experience in simulating the execution of AI applications on complex systems, identify bottlenecks and deploy hardware and software optimization strategies.

Hands-on session - Hermes Demonstrator - Linearization of radio frequency power amplifiers

A novel concept for linearization of Radio Frequency (RF) Power Amplifiers (PAs) will be presented. The Walsh Transform is used for both a conversion scheme from digital to analogue and as a computational basis for evaluating a digital PA predistorter (DPD) model. The mathematical properties of the Walsh theory are exploited to enhance the convergence speed of conventional DPD algorithms and reduce their computational complexity. An experimental demonstration exhibits the performances of a broadband PA’s DPD with simulations and measurements results of a 3-4GHz PA. For similar accuracy, the proposed method converges as fast as conventional algorithms with linear computational complexity instead of quadratic one.

Speakers

› Alireza Amirshahi: École polytechnique fédérale de Lausanne, Switzerland

› Giovanni Ansaloni: École polytechnique fédérale de Lausanne, Switzerland

› Didier Belot: CEA-Leti, Grenoble, France

› Emilio Calvanese: CEA-Leti, Grenoble, France

› Nathalie Deltimple: University of Bordeaux, France

› Marina Deng: University of Bordeaux, France

› Maxandre Fellmann: University of Bordeaux, France

› Magalie de Matos: University of Bordeaux, France

› Rafael Medina Morillas: EPFL Lausanne, Switzerland

› Valentin Meunier: IMS Bordeaux, France

› Thomas Mikolajick: Scientific Director, NaMLab GmbH and Professor for nanoelectronic materials, TU Dresden, Germany

› Alice Mizrahi: Thales TRT, France

› Chhandak Mukherjee: University of Bordeaux, France

› Michel Paindavoine: Yumain, France

› Sylvain Pelloquin: LAAS-CNRS, Toulouse, France

› François Rivet: University of Bordeaux, France

› Jean-Luc Rouas: University of Bordeaux, France

› Gerhard Rzepa: GGlobal TCAD Solutions GmbH, Austria

› Sylvain Saïghi: University of Bordeaux, France

› Christian Schleich: GGlobal TCAD Solutions GmbH, Austria

› Adrien F. Vincent: University of Bordeaux, France

› Giovanni Ansaloni: École polytechnique fédérale de Lausanne, Switzerland

› Didier Belot: CEA-Leti, Grenoble, France

› Emilio Calvanese: CEA-Leti, Grenoble, France

› Nathalie Deltimple: University of Bordeaux, France

› Marina Deng: University of Bordeaux, France

› Maxandre Fellmann: University of Bordeaux, France

› Magalie de Matos: University of Bordeaux, France

› Rafael Medina Morillas: EPFL Lausanne, Switzerland

› Valentin Meunier: IMS Bordeaux, France

› Thomas Mikolajick: Scientific Director, NaMLab GmbH and Professor for nanoelectronic materials, TU Dresden, Germany

› Alice Mizrahi: Thales TRT, France

› Chhandak Mukherjee: University of Bordeaux, France

› Michel Paindavoine: Yumain, France

› Sylvain Pelloquin: LAAS-CNRS, Toulouse, France

› François Rivet: University of Bordeaux, France

› Jean-Luc Rouas: University of Bordeaux, France

› Gerhard Rzepa: GGlobal TCAD Solutions GmbH, Austria

› Sylvain Saïghi: University of Bordeaux, France

› Christian Schleich: GGlobal TCAD Solutions GmbH, Austria

› Adrien F. Vincent: University of Bordeaux, France

Feedback

"Just got back from the IMS E3AI summer school,the welcome was amazing, and the technical program engaging. Highly recommend to anyone passionate about AI!" "Had an amazing week at IMS E3AI summer school. The technical program was top-notch. The lecturers were knowledgeable and approachable, making learning even more enjoyable. Social activities were well-organized !" "Participating in IMS E3AI summer school was a nice experience. The organizers did a remarkable job welcoming us, and the technical program was intense !" "The technical courses were impressive. The atmosphere created by the organizers made the week memorable. The relaxation moments and social activities complemented the technical program. Big thanks to all organizers and speakers!" |